SLT3G1

Talented design team, ASIC and PMIC

Bouton

Titre de la diapositive

Our design methodology enables IP high reuse rate and wide test coverage

Bouton

Titre de la diapositive

PMIC IP portfolio covering desgin needs

Bouton-

Titre de la diapositive

Consult our latest mixed signal IPs: A high accuracy PFD in 22nm FDSOI

Bouton

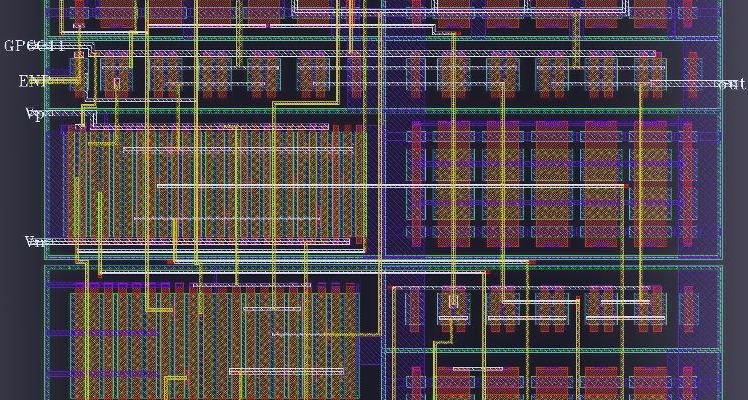

Silicon IC design

Capabilities

- Wide offer of Analog & Mixmode IPs

- In-house Test oriented PDK

- In-house IP management server

- Highly talented team

Design Services

- Full custom ASICs and PMICs

- Advanced PMIC Silicon definition

- Advanced Clock Synthesis IPs

- Advanced Analog IPs

- Matrix IP integration

New IPs (Browse our latest IP developments)

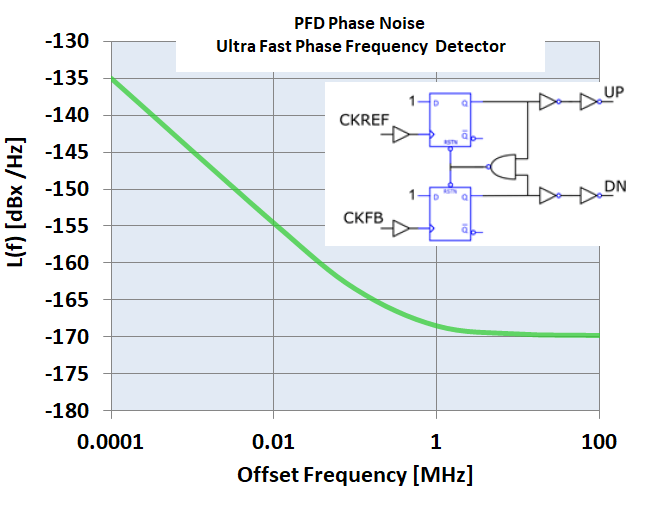

22nm FDSOI Phase Frequency Detector

Our latest design of a 3-state Phase Frequency Detector shows state of the art phase-noise performance and a very high immunity to power supply noise.

This IP has been designed in both bulck 22nm CMOS and FDSOI 22nm nodes where it shows substantial improvement of phase noise.

Our PFD design exploits the extremely high speed propagation delays possible with 22nm FDSOI digital cells, knowing that we redesigned the D flip-flops in order to achieve 1 single gate propagation delay (27ps) and an extremely low phase noise.

High Side floating 1.8V Voltage Regulator

A floating 0-20V power domain high side 1.8V Voltage Regulator, specifically designed to power low consumption floating Analog IPs.

Deliveries available :

- Process HV-BiCMOS 0.18um

- VerilogA Model

- Schematic, Layout, Abstract

- Automated AC, DC, TRAN, MC test scripts (Ocean, Skill++)

- Silicon proof

Silicon IPs & Design Services (browse our portfolio of IPs, ICs, & design tools)

ASIC integration / finishing

We possess a long track record as independent design center in the ASIC and PMIC design area.

We have developped a strong portfolio of IPs and design Tools since 2011 and performed 20+ ASIC/PMIC tapeouts:

- HF switched PMIC (2X 16MHz Buck)

- Neural Stim. ASIC (HV BiCMOS)

- High res matrix ADC (130nm)

- Wideband PLL (FDSOI 22nm)

This is possible thanks to our continuous training program offered to our engineers at all level of productivity.

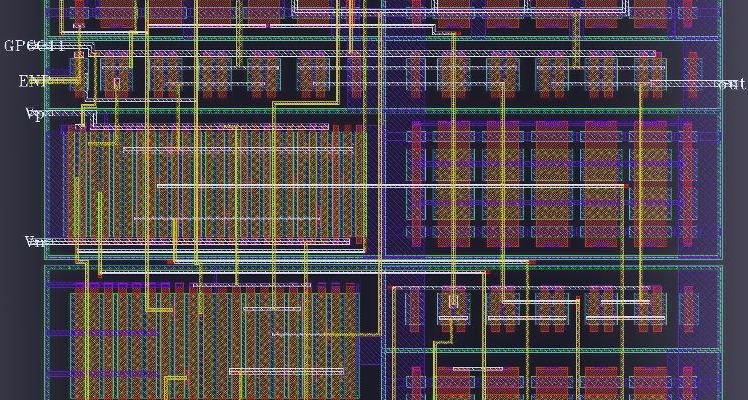

Analog / Mixmode IPs

Analog / Mixmode IPs

- 8-bit current steering DAC (0.25LSB, 10MHz)

- Bandgap reference voltage providing 600mV +/-3%, 4-bit trim, non-buffered, 5.5V

- Floating 1.8V LDO power +/-10V

- 20GHz PFD (FDSOI)

- Precision RC oscillator, 9MHz +/-1%, 5-bit trim, 1.8V

- Rail-to-rail precision OTA (5.5V)

Contact us for detailed portfolio

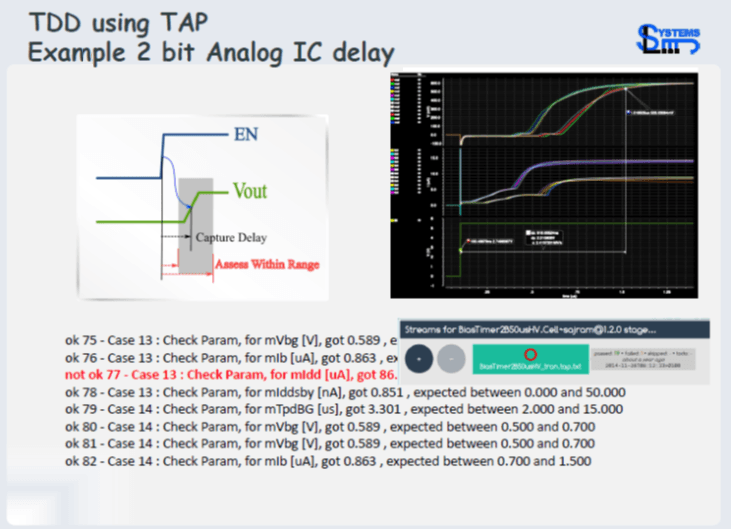

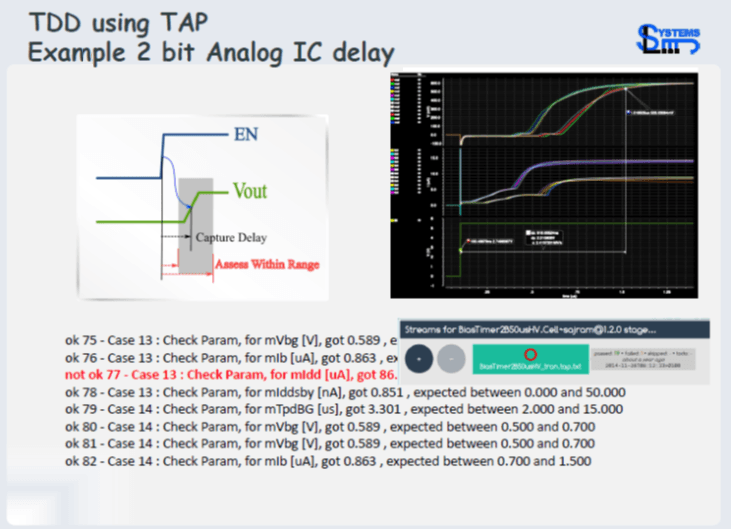

Unit Test PDK

Unit Test PDK

Fruit of 6 years of R&D, our PDK has been developped in SKILL++ / Ocean / VerilogA / Verilog / Perl / Bash to automate Analog & Mixed signal IP testing and characterization.

Our PDK enables a stronger ReUse strategy for much lower cost than many sophisticated GUI editors

SYNAV™ :

A Corporate Level

Design Collaboration Server

SYNAV™ leads your company servers to handle your Product or IP Creation procedures, Specifications, and way beyond!

SYNAV™ is empowered by an abstract model to handle any type of Engineering Domain.

SYNAV™ is a light but powerful design collaboration server enabling live collaboration between design engineers during product development:

- Live documentation

- Version management

- IP portfolio management

- Design documentation

- Team collaboration

- IP test stream

Copyright SL3J SYSTEMS. All Rights Reserved | Privacy policy | Cookie policy | Terms of use | Terms of sale